# Structera™ X 2404 Memory-Expansion Controller

CXL 2.0 DDR4 4-channel expander P/N MV-SLX24041-A0-HF340AA-C000

#### **Overview**

The Marvell® Structera™ X 2404 (P/N MV-SLX24041-A0-HF340AA-C000) device is a CXL memory-expansion controller designed to enhance memory scalability and performance in data center environments. The Structera X 2404 supports DDR4 with three DIMMs per channel, enabling a total of 12 DDR4 DIMMs per controller to maximize memory capacity. This configuration optimizes resource utilization, seamlessly integrates with existing server systems and reduce electronic waste by enabling the use of recycled DDR4 memory modules.

Products in the Structera X memory-expansion controller family are CXL 2.0 compliant and support 16 PCIe/CXL lanes for a single host or bifurcation to eight PCIe/CXL lanes for dual-host configurations.

The Structera X 2404 offers four inline LZ4 compression engines that support four channels of DDR4-3200 at full bandwidth. The compression engines support both 4KB and 1KB page sizes.

Structera X devices support inline AES-XTS 256-bit encryption and decryption, ensuring robust data security with high-performance encryption algorithms for sensitive.

Structera X devices integrate an embedded hardware security module (eHSM) for system-level security. The eHSM securely manages cryptographic keys and provides hardware-based authentication. Coupled with secure boot capabilities, the eHSM ensures that only trusted firmware and software are loaded during system startup, safeguarding against unauthorized access and potential threats.

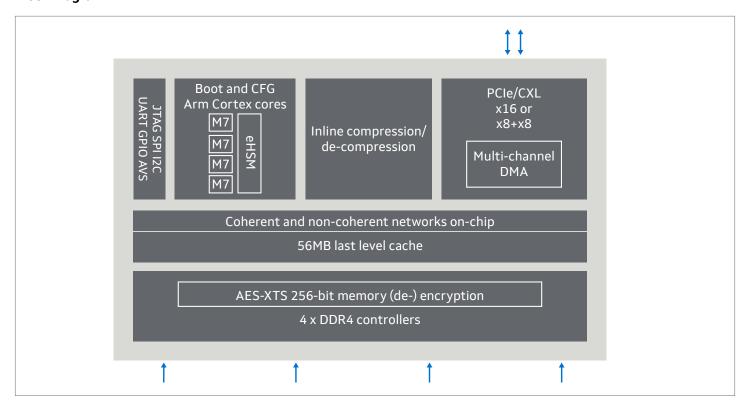

#### **Block Diagram**

### **Key Features**

| Features                 | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standards and interfaces | <ul> <li>PCIe 5.0 (2.5/5.0/8.0/16.0/32.0 GT/s)</li> <li>CXL 2.0 (8.0/16.0/32.0 GT/sec)</li> <li>PCIe/CXL host interfaces</li> <li>16-lane physical interface (PHY)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                   |

| CXL modes                | <ul> <li>CXL 1.1 Exclusive Restricted CXL Device (eRCD) mode</li> <li>Power-saving modes</li> <li>Lane-reversal</li> <li>Spread-spectrum clocking for common reference-clock links</li> <li>QoS telemetry</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| Memory                   | <ul> <li>Support for DDR4: <ul> <li>Up to 3200 MT/s data rate with 2DPC</li> <li>Up to 1600 MT/s data rate with 3DPC</li> <li>Subdivided into two 72-bit subchannels (64 data bits, eight ECC bits)</li> <li>Up to three DIMMs per channel</li> <li>Up to six physical ranks per subchannel</li> </ul> </li> <li>U/R/LRDIMM and soldered DRAM</li> <li>DRAM interfaces with enhanced RAS capabilities</li> <li>MPAM support for bandwidth partitioning and monitoring</li> <li>DRAM crypto with AES-XTS 256 on data with optional address scrambling</li> </ul> |

| Control and management   | <ul> <li>Miscellaneous I/O interfaces: SPI/QSPI/xSPI, GPIO, UART, I3C, TWSI, I2C/SMBus</li> <li>Multiple embedded Arm Cortex M7 processors</li> <li>System-control processor (SCP)</li> <li>Management-control processor (MCP)</li> <li>Cryptographic-control processor (CCP)</li> <li>PCle configuration-off oad processor (PCP)</li> <li>Embedded hardware security module (eHSM) using Arm Cortex M3 processor</li> <li>Extensive power and thermal management capabilities</li> <li>Compatible with Arm Server Base System Architecture (SBSA)</li> </ul>   |

| Compression              | <ul> <li>Support for four channels of DDR4-1600 at 100% bandwidth</li> <li>Support for 4K or 1K page sizes</li> <li>LZ4 algorithm support</li> <li>Data integrity protection, including poison and decompress-after-compress</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| Package characteristics  | • 55mm x 34mm package with 0.65 mm ball pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## **Target Applications**

- · In-memory databases

- · Design simulation

- · Deep learning

To deliver the data infrastructure technology that connects the world, we're building solutions on the most powerful foundation: our partnerships with our customers. Trusted by the world's leading technology companies over 25 years, we move, store, process and secure the world's data with semiconductor solutions designed for our customers' current needs and future ambitions. Through a process of deep collaboration and transparency, we're ultimately changing the way tomorrow's enterprise, cloud, automotive, and carrier architectures transform—for the better.

$Copyright @ 2024\ Marvell.\ All\ rights\ reserved.\ Marvell\ and\ the\ Marvell\ logo\ are\ trademarks\ of\ Marvell\ or\ its\ affiliates.\ Please\ visit\ \underline{www.marvell.com}\ for\ a\ complete\ list\ of\ Marvell\ trademarks.\ Other\ names\ and\ b\ rands\ may\ b\ claimed\ as\ the\ property\ of\ others.$